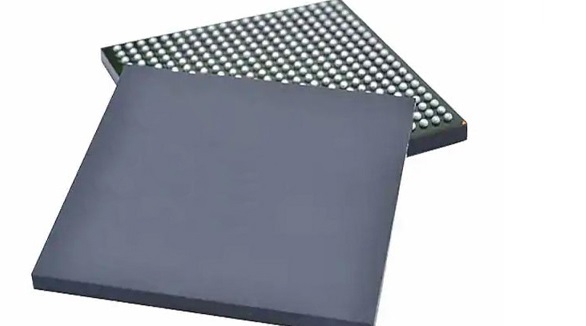

Package on Package (PoP) Assembly

Package on Package (PoP) assembly stacks semiconductor devices vertically, enhancing space efficiency and performance in electronics with design flexibility.

Miniaturization and performance-enabling technologies are crucial in today's fast-moving electronics world. One such technology is Package on Package (PoP) assembly, which is a method of integrated circuit packaging in which multiple semiconductor devices are stacked vertically. The interconnections in this technique are made with solder balls, enabling more component density and better electrical performance. This paper explains the basics of PoP technology, the process chain of its assembly, advantages, challenges, applications, and future trends.

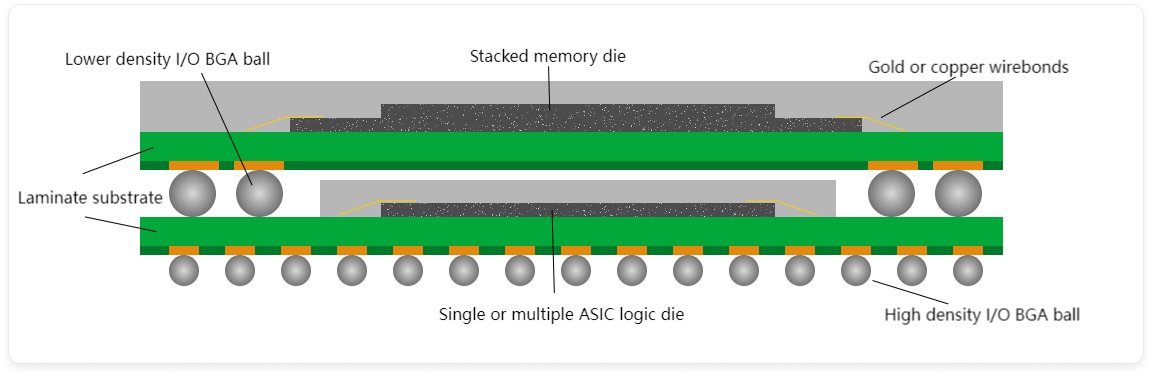

Package on Package, as the name suggests, requires stacking two or more completely packaged devices into a single vertical unit. Here are some key aspects of PoP:

Each device is independently packaged before the PoP assembly.

Devices are connected via solder balls or bumps

The bottom device is named the 'base package'.

The stacked device above it is called the 'top package'.

An interposer can be used between packages to enable connection reroutes.

The overall PoP structure is treated as a single integrated component.

This technology is sometimes referred to using either of the terms, package-on-package or package-over-package.

Why PoP is Used?

PoP technology has gained traction due to several compelling benefits:

Space Efficiency

The key benefit of PoP assembly is that it saves space on the motherboard. By directly stacking the memory package over the processor package, PoP reduces the general footprint of electronic components. It becomes a perfect choice for those devices in which space is the critical factor, including smartphones, tablets, and other portable electronic devices.

Flexible Design

PoP technology offers design and manufacturing flexibility. Because the individual packages can be tested separately before assembly, yield is improved and time to market is reduced. Manufacturers can mix and match various semiconductor components to optimize performance, which opens up more versatile and adaptive product development.

Improved Performance

Stacking memory right on the processor reduces latency, since that reduces the distance the electrical signals have to travel. This can easily translate to faster data processing speeds and overall system performance, beneficial in applications where high speeds of data handling are required.

Simplified Assembly

By integrating more components in one stacked assembly, PoP simplifies the overall design. It lessens the complexity of the main PCB layout, thereby reducing manufacturing and assembly costs of PCBs.

PoP Components

PoP assembly majorly consists of two types of packaged components:

Base Package

Generally includes high pin count devices such as processors.

Offers mechanical support for the stacked structure.

Manufactured using conventional packages such as FBGA, PBGA, or LGA

Has a high-density array of solder balls/ bumps on top

Top Package

Usually a memory device like DRAM or flash

Housed in packages such as TSOP, CSP, or wafer-level CSP.

Smaller and with solder balls on the bottom-side

Interposer

Extra substrate between base and top package

Allows for I/O rerouting and ball grid array density optimization.

PoP Manufacturing Process

The PoP assembly process involves several key stages:

Sourcing Packaged Components: Acquire fully packaged and compatible base and top devices.

Applying Solder Paste: Dispense solder paste on the base package using a stencil. It may also be applied to the top package.

Placing Base Package: Mount the base package on the PCB through standard SMT processes.

Attaching Top Package: Position the top package over the base with precision, aligning solder balls to corresponding pads.

PoP Reflow: Reflow the assembly into solid solder joints using specialized thermal profiles.

Underfill Dispensing: Provide underfill material to enhance mechanical stability and protect solder joints from environmental hazards.

Conformal Coating: The coating enhances reliability and environmental resistance of the assembly.

PoP Design Considerations

The major considerations for effective PoP design encompass the following aspects:

Package Selection: Compatibility in terms of height, ball pitch, and CTE, which should be compatible to conform to the design constraints.

Electrical Design: Optimization of connectivity, signal routing, and thermal management.

PCB Land Pattern Design: Providing appropriate pad sizes and clearances for BGA packages.

Solder Paste Stencil Design: Determining proper aperture sizes and stencil configurations.

Process Considerations: Reflow profile balancing and warpage minimization.

Challenges and Limitations

Even with the advantages, PoP assembly has some challenges. Among them are the following:

Thermal Management: Reliability depends on managing CTE mismatches and thermal stresses.

Process Complexity: Reflow profile optimization and managing underfill variations require tight process control.

Warpage and Inspectability: Balancing layers to reduce warpage and using X-ray for inspection can complicate the process.

PoP Applications

Consumer Electronics

The most common application for PoP technology is found within consumer electronics, such as mobile devices like smartphones and tablets. These devices use space and performance-enhancing functionalities provided by PoP in order to house more powerful capabilities within a small enclosure.

Wearable Devices

Wearable technology, such as smartwatches and fitness trackers, also makes use of PoP assembly. In these compact gadgets, space efficiency with PoP is important to fit more features in smaller and lighter forms.

Automotive Electronics

PoP finds its application in ADAS and infotainment systems within the automotive industry. These applications require high processing with reliability, something that PoP technology can offer.

Internet of Things (IoT)

The IoT ecosystem increasingly relies on PoP technology to build compact, efficient, and powerful devices. Sensors, home automation devices, and connected gadgets all benefit from the high-density performance capabilities that PoP has to offer.

The Future of PoP

Emerging trends in PoP technology are toward enhancing its capabilities further:

Hybrid Configurations: Incorporation of passives and sensors with active ICs Advanced Interposers: Development of ultra-thin wafer-level CSPs and silicon interposers.

Innovative Materials: Adoption of novel conductive adhesives for improved interconnections.

High-Performance Integration: Applications in computing and networking, utilizing ultra-fine pitch PoP.

Package-on-Package represents a powerful approach to PCB design, enabling continued miniaturization and performance optimization in electronic systems through vertical stacking. As technology evolves, PoP is poised to play a crucial role in the future of electronics design, offering solutions that enhance both functional capability and manufacturing efficiency.

Hot Tags:

Contact us

If you can't find what you're looking for, please contact us.

Article

The article compares Ball Grid Array (BGA) and Land Grid Array (LGA) packaging technologies for mounting microprocessors on PCBs. It details their pros and cons, applications, and factors to consider for optimal design choices.

Through-Hole Technology (THT) mounts electronic components by inserting their leads through pre-drilled PCB holes and soldering them. While durable and ideal for harsh conditions, THT is less space-efficient than SMT.

Compared to THT, SMT offers better miniaturization and weight reduction in any electronic application. With the use of BGA packages, high-assembly density, reliability, and improved performance are achieved; on the other hand, this requires a rework and inspection that is not really common. PCBX specializes in the area of advanced SMT and BGA assembly to help drive modern requirements of compact electronic devices.